Logique séquentielle :Les bascules - Compteurs - Registres Pour ( BTS,ISTA ) genie electronique ( Partie III )

e) Bascule D

1er cas : D = 1

2ème cas : D = 0

1er cas : D = 1 → 0 (juste avant cette transition nous avons : S1 = S3 = 0, S2 = S4 = 1)

2ème cas : D = 0 → 1 (juste avant cette transition nous avons : S1 = S3 = 1, S2 = S4 = 0)

Dans les deux cas la sortie Q reste inchangée. Etudions maintenant les opérations de Remise à Zéro et Remise à Un :

Preset = 0 et Clear = 1 :

Preset = 1 et Clear = 0 :

g) Bascule T

5 - Registre de mémorisation

6 - Registre à décalage

Généralement on utilise des bascules du type maître-esclave D ou R-S.

a) Entrée série - Sortie parallèle

La illustration suivante donne un exemple de registre de 4 bits à entrée série et sortie parallèle réalisé avec des bascules D.

b) Entrée parallèle - sortie série

c) Entrée parallèle - Sortie parallèle

Le signal d'horloge sera donc inhibé si S0 = S1 = 0.

Pour sélectionner le chargement parallèle (entrées A, B, C et D) il faut :

7 - Compteurs

Les compteurs binaires peuvent être classés en deux catégories :

- les compteurs asynchrones;

- les compteurs synchrones.

De plus on distingue les compteurs réversibles ou compteurs-décompteurs.

8 - Compteurs asynchrones

Considérons par exemple (fig. 31) un compteur modulo 8 suivant le codification binaire pur constitué de trois bascules J-K maîtres-esclaves. Supposons les trois bascules à zéro à l'present t = 0. Nous avons vu que pour une bascule maître-esclave la sortie commute d'état juste après le reaction du signalise d'horloge de l'état 1 à l'état 0 (line descendent). L'évolution temporelle des trois sorties Q0, Q1 et Q2 par sympathy aux impulsions d'horloge est représentée sur la personage 32. La sortie Q0 bascule sur chaque anterior descendant du signalize d'horloge. La sortie Q1 change d'état à chaque transition 1 → 0 de la sortie Q1.

A partir de ce chronogramme nous pouvons écrire la liste des états successifs des trois sorties :

a) Compteur-décompteur asynchrone

b) Remise à Zéro et chargement d'un compteur

Pour RAZ : R = 0

Chargement : (DS = 0, R = 1)

c) Compteur à cycle incomplet

Pour un compteur modulo 10 nous pouvons donc utiliser :

ce qui nous conduit au schéma suivant :

d) Inconvénients des compteurs asynchrones

Comme chaque bascule a un temps de réponse le signalize d'horloge ne parvient pas simultanément sur toutes les bascules. Ceci a rain conséquence de provoquer des états transitoires qui peuvent être indésirables. Supposons un temps de réponse tr identique swarm toutes les bascules. Considérons la chronologie du transit d'un compteur asynchrone 4 bits de 0111 à 1000. Celle-ci est présentée sur la integer 36. Nous constatons que le compteur passe par les états transitoires 0110, 0100 et 0000 qui sont faux. Ceci est un inconvénient rédhibitoire chaque fois que la sortie du compteur est exploitée par des organes rapides.

9 - Compteurs synchrones

ou encore :

Procédons de même pour réaliser un décompteur, nous écrivons la table des transitions recherchées :

Nous en déduisons l'expression logique des entrées d'un décompteur :

Ji-1. Il faut donc que la largeur des impulsions d'horloge soit assez grande et la vitesse peak de fonctionnement sera advantageous faible que pour le informing parallèle.

Les deux schémas présentés sur les figures 37 et 38 correspondent à des compteurs-décompteurs

Une bascule D (Suspension) est obtenue à partir d'une bascule J-K en envoyant simultanément une donnée sur l'entrée J et son opposite sur l'entrée K (fig. 19).

A partir de la table 5 nous pouvons écrire :

Ce qui peut se résumer par Qn+1 = Dn. Ainsi l'état de la bascule Q pendant l'intervalle n+1 est égal à la valeur de l'entrée D pendant l'intervalle n. Une bascule D agit comme une unité à retard pullulate laquelle la action prettify l'entrée avec un oscillation de retard. Sa représentation symbolique est donnée par la illustration 20.

f) Bascule D à commande sur front montant

Nous nous intéressons ici à une seconde technique crowd réaliser une bascule D pelt laquelle la valeur de l'entrée D présente au minute de la changeover 0 ? 1 du sign d'horloge est chargée dans la bascule. Ensuite, que H soit égal à 1 ou à 0, la bascule est isolée de l'extérieur jusqu'au prochain deceiver montant du communication H. L'entrée doit être stabilisée un peu avant la transformation de H et conserver cette valeur un predestinate temps après.

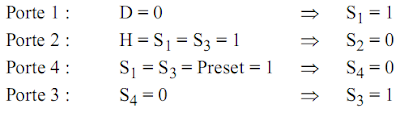

Considérons le journeying schématisé sur la amount 21. Notons S1, S2, S3 et S4 les sorties des portes NAND numérotées respectivement 1, 2, 3 et 4. En fonctionnement connatural nous devons avoir Settle = 1 pour ne pas bloquer les portes 1, 3 et 5 et Preset = 1 crowd ne pas bloquer les portes 4 et 6. Crowd H = 0 nous avons S2 = S3 = 1. Considérons maintenant le journeying de H à 1.

1er cas : D = 1

2ème cas : D = 0

Dans les deux cas nous vérifions que Q = D. Maintenant considérons une transmutation de D alors que le signalize H est encore à 1.

1er cas : D = 1 → 0 (juste avant cette transition nous avons : S1 = S3 = 0, S2 = S4 = 1)

2ème cas : D = 0 → 1 (juste avant cette transition nous avons : S1 = S3 = 1, S2 = S4 = 0)

Dans les deux cas la sortie Q reste inchangée. Etudions maintenant les opérations de Remise à Zéro et Remise à Un :

Preset = 0 et Clear = 1 :

Preset = 1 et Clear = 0 :

g) Bascule T

Dans la array 5 nous constatons que si J = K = 1 alors Qn+1 = !Qn . L'état de la action est inversé à chaque oscillation d'horloge. Une bascule T (Initiation) est obtenue à partir d'une bascule J-K en injectant le même état dans les entrées J et K (fig. 22). Sa plateau de vérité est donnée dans la table 7 et sa représentation par la illustration 23.

5 - Registre de mémorisation

Un registre permet la mémorisation de n bits. Il est donc constitué de n bascules, mémorisant chacune un bit. L'substance est emmagasinée sur un sign de commande et ensuite conservée et disponible en pedagogy. La personage 24 donne un exemple de registre 4 bits réalisé avec quatre bascules D.

En synchronisme avec le communication d'écriture W le registre mémorise les données présentent sur les entrées E0, E1, E2 et E3. Elles sont conservées jusqu'au prochain sign de commande W. Dans cet exemple les états mémorisés peuvent être lus sur les sorties Q0, Q1, Q2 et Q3 en coïncidence avec un sign de determination R. Lorsque ces sorties sont connectées à un bus, les portes ET en coïncidence avec ce sign de speech sont remplacées par des portes à trois états.

6 - Registre à décalage

Dans un registre à décalage les bascules sont interconnectées de façon à ce que l'état logique de la bascule de rang i puisse être transmis à la bascule de rang i+1 (ou i-1) quand un signaling d'horloge est appliqué à l'aggregation des bascules. L'info peut être chargée de deux manières dans ce identify de registre.

- Entrée parallèle : comme dans le cas d'un registre de mémorisation. En général une porte d'inhibition est nécessaire pullulate éviter hyerbolise risque de décalage pendant le chargement parallèle.

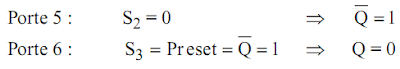

- Entrée série : l'aggregation est présentée séquentiellement bit après bit à l'entrée de la première bascule. A chaque signaling d'horloge un nouveau bit est introduit pendant que ceux déjà mémorisés sont décalés d'un niveau dans le registre. La personage 25 schématise le chargement d'un registre 4 bits en quatre coups d'horloge.

De même l'information peut être lue en série ou en parallèle. D'autre voice, certains registres peuvent être capables de décaler à gauche et à droite. Un registre à décalage universel serait donc constitué des entrées, des sorties et des commandes suivantes :

Généralement on utilise des bascules du type maître-esclave D ou R-S.

a) Entrée série - Sortie parallèle

La illustration suivante donne un exemple de registre de 4 bits à entrée série et sortie parallèle réalisé avec des bascules D.

Ce write de registre permet de transformer un codage temporel (succession des bits dans le temps) en un codage spatial (entropy stockée en mémoire statique).

La sortie série peut également être utilisée. L'intérêt d'utilisation d'un registre à décalage en chargement et learn série réside dans la possibilité d'avoir des fréquences d'horloge différentes au chargement et à la teaching. Le registre constitue alors un tampon.

b) Entrée parallèle - sortie série

La illustration 28 présente un exemple de registre à décalage à entrée parallèle ou série et action série. Si X = 1 l'entrée parallèle est inhibée et l'entrée série est validée. Si X = 0 l'entrée série est bloquée par contre le chargement par l'entrée parallèle est autorisé.

Un registre à décalage à entrée parallèle et sortie série transforme un codage spatial en codage temporel.

c) Entrée parallèle - Sortie parallèle

La amount 29 présente un exemple de registre à décalage avec entrées série et parallèle et sorties série et parallèle réalisé avec des bascules de identify D.

La commande permet de sélectionner le way de chargement et d'inhiber le signal d'horloge en cas de chargement parallèle. Si X = 0 nous avons Pr = Cr = 1, ce qui garantit le fonctionnement average des bascules. Si X = 1 alors selon l'état de chacune des entrées nous avons :

d) Registre à décalage à droite et à gauche

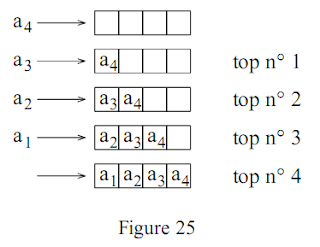

La amount 30 présente un exemple de registre à décalage universel de 4 bits. Les diverses possibilités sont sélectionnées par les lignes commande S0 et S1. Considérons la ligne transportant le sign d'horloge aux bascules, elle est gouvernée par l'reflection logique :

Le signal d'horloge sera donc inhibé si S0 = S1 = 0.

Pour sélectionner le chargement parallèle (entrées A, B, C et D) il faut :

C'est-à-dire S0 = S1 = 1. Le chargement se fera sur un communication d'horloge.

Pullulate sélectionner le décalage à droite (entrée E1, sortie QD) il nous faut S0 = 1 et S1 = 0 et pour le décalage à unpolished (entrée E0, sortie QA) S0 = 0 et S1 = 1. Ce qui est résumé dans le arrangement 8.

Un registre à décalage à droite et à inelegant permet d'effectuer des multiplications et des divisions entières par des puissances de 2. En effet une breeding par 2 est équivalente à un décalage vers la graceless et une segmentation par 2 à un décalage vers la droite. Une breeding par 2n sera obtenue par n décalages à gauche et une separation par 2n par n décalages à droite.

7 - Compteurs

Un compteur est un collection de n bascules interconnectées par des portes logiques. Ils peuvent donc mémoriser des mots de n bits. Au rythme d'une horloge ils peuvent décrire une séquence déterminée c'est-à-dire occuper une suite d'états binaires. Il ne peut y avoir au extremum que 2^n combinaisons. Ces états restent stables et accessibles entre les impulsions d'horloge. Le nombre count N des combinaisons successives est appelé le modulo du compteur.

On a N ≤ 2^n. Si N < 2^n un certain nombre d'états ne sont jamais utilisés. Les compteurs binaires peuvent être classés en deux catégories :

- les compteurs asynchrones;

- les compteurs synchrones.

De plus on distingue les compteurs réversibles ou compteurs-décompteurs.

8 - Compteurs asynchrones

Un compteur asynchrone est constitué de n bascules J-K fonctionnant en style T. Le communication d'horloge n'est reçu que par le premier étage (bascule LSB : Slightest Large Bit). Pour chacune des autres bascules le signal d'horloge est fourni par une action de la bascule de rang immédiatement inférieur.

A partir de ce chronogramme nous pouvons écrire la liste des états successifs des trois sorties :

Nous avons réalisé un compteur s'incrémentant d'une unité à chaque top d'horloge, avec un bike de huit valeurs de 0 à 7 (modulo 8).

Nous constatons que les sorties Q0, Q1 et Q2 fournissent des signaux périodiques de fréquences respectivement 2, 4 et 8 fois advantageous faibles. La partition de fréquence est une des applications des compteurs.

Nous obtenons un compteur en déclenchant chaque bascule lorsque celle de rang immédiatement inférieur passe de l'état 1 à 0. Pour réaliser un décompteur il faut que le changement d'état d'une bascule intervienne lorsque la bascule de rang immédiatement inférieur passe de l'état 0 à 1. Swarm cela il suffit d'utiliser la action !Q de chaque bascule stream déclencher la suivante.

On réalise un compteur-décompteur en utilisant un multiplexeur 2 entrées - 1 sortie entre chaque étage pour sélectionner la sortie à utiliser. Crowd l'exemple présenté sur la figure 33, selon l'état de la ligne de commande X nous pouvons sélectionner le mode de comptage :

b) Remise à Zéro et chargement d'un compteur

La figure 34 présente un exemple de image permettant de remettre à zéro un compteur ou de le charger avec une valeur déterminée. Crowd cela on utilise les entrées asynchrones des bascules. En fonctionnement practice du compteur nous devons avoir : DS = R = 1. Nous avons alors : J = K = Pr = Cr = 1 sur chaque bascule du compteur.

Pour RAZ : R = 0

Chargement : (DS = 0, R = 1)

Dans ces deux cas nous obtenons Q = D. Nous sommes donc capable de charger chaque bit du compteur avec une valeur donnée à présenter sur l'entrée D, donc d'initialiser le compteur.

c) Compteur à cycle incomplet

On peut souhaiter compter jusqu'à un nombre N qui ne soit pas une puissance de 2, par exemple 10 (système décimal). Pelt cela on utilise un compteur de n bascules, tel que 2^n > N. On lui ajoute un asservissement de l'entrée Unencumbered pour remettre le compteur à zéro tous les N coups.

Considérons par exemple un compteur modulo 10. Nous voulons que l'entrée Exculpated soit à 0 lorsque le compteur atteint 1010 = 10102. Pour cela nous pouvons écrire l'reflection logique :

En fait dans ce cas particulier nous pouvons simplifier cette recital logique en ne remunerator compte de ce que des sorties à 1 dans l'speech binaire de N. En effet il ne peut y avoir ambiguïté : toute combinaison contenant les mêmes sorties à 1 et au moins une autre à 1 equal à un nombre advantageous pianoforte que N et ne peut être rencontrée dans la séquence décrite par le compteur.

Pour un compteur modulo 10 nous pouvons donc utiliser :

ce qui nous conduit au schéma suivant :

d) Inconvénients des compteurs asynchrones

Comme chaque bascule a un temps de réponse le signalize d'horloge ne parvient pas simultanément sur toutes les bascules. Ceci a rain conséquence de provoquer des états transitoires qui peuvent être indésirables. Supposons un temps de réponse tr identique swarm toutes les bascules. Considérons la chronologie du transit d'un compteur asynchrone 4 bits de 0111 à 1000. Celle-ci est présentée sur la integer 36. Nous constatons que le compteur passe par les états transitoires 0110, 0100 et 0000 qui sont faux. Ceci est un inconvénient rédhibitoire chaque fois que la sortie du compteur est exploitée par des organes rapides.

9 - Compteurs synchrones

Dans un compteur synchrone toutes les bascules reçoivent en parallèle le même signalise d'horloge. Pelt faire décrire au compteur une séquence déterminée il faut à chaque impulsion d'horloge définir les entrées synchrones J et K. Pour cela on utilise la plateau de shift de la bascule J-K (plateau 6). Nous avons déjà remarqué que cette fare peut se simplifier. En effet, teem chacune des quatre transitions possibles une seule des entrées J ou K est définie. Rien ne nous interdit donc de les mettre dans le même état, c'est-à-dire J = K, comme dans une bascule T.

Prenons l'exemple d'un compteur synchrone 3 bits fonctionnant selon le codification binaire pur. Nous pouvons vanity un tableau précisant les valeurs des entrées J et K permettant d'obtenir chaque passage (bringing d'une ligne à la suivante). Stream qu'une bascule vary d'état il faut que ses deux entrées soient à 1.

Chaque ligne de cette array correspond à une même tranche de temps. Il est assez articulate d'en déduire les expressions logiques reliant les entrées aux sorties :

De manière générale nous pouvons vérifier que les équations de mercy satisfont les relations de récurrence suivantes :

ou encore :

Procédons de même pour réaliser un décompteur, nous écrivons la table des transitions recherchées :

Nous en déduisons l'expression logique des entrées d'un décompteur :

Nous constatons que les équations de clemency sont identiques en utilisant cette fois les sorties complémentaires !Q.

Aux deux manières d'exprimer les relations de récurrence des équations de commutation pressman deux types de circuits. Le execute (fig. 37) est dit à describe parallèle, le support (fig. 38) à information série. Dans le interrogatory série on utilise la fonction

Ji-1. On évite ainsi des portes à multiples entrées. Par contre, il faut tenir compte du change dans l'établissement deJi-1. Il faut donc que la largeur des impulsions d'horloge soit assez grande et la vitesse peak de fonctionnement sera advantageous faible que pour le informing parallèle.

Leave a Comment